설치된 실행파일을 실행

Welcome창은 닫고 다음과 같은 화면이 출력

프로젝트 생성 : File -> New -> Project

적절한 새 프로젝트 이름 설정

새 파일 만들기 : Create New File 클릭

① 적절한 새 파일 이름 설정 (.v - Verilog 파일 확장자)

② Verilog 언어를 사용 (※VHDL -> Verilog 변경※)

생성한 프로젝트에 추가된 파일을 확인

Add items to the Project 창은 종료

추가된 파일을 더블 클릭하면

코드를 작성할 수 있는 공간이 생성됨

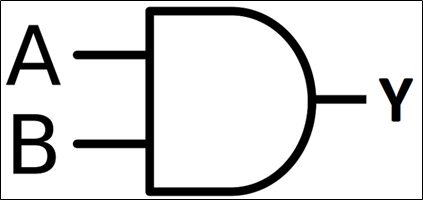

Verilog 언어로 AND 모듈을 설계

Verilog 코드 작성

module AND(input a,b, ouput y); // 모듈선언, 모듈이름, 모듈 입출력조건(입력 A,B 출력 Y)

assign y = a*b; // 두 입력을 곱하여 출력

endmodule // 모듈종료

Verilog언어로 코드를 작성 후 Ctrl+s를 눌러 저장

AND모듈을 설계하였다.

작성한 AND모듈의 기능 테스트를 위하여 테스트벤치 작성

테스트벤치 코드 또한 Verilog 파일이므로 새 파일 추가적으로 생성

테스트벤치 (새 파일) 생성 : 마우스 우클릭 -> Add to Project -> New File

① 파일 이름 : 모듈이름_testbbench 설정(AND_testbench.v)

②Verilog 언어를 사용 (※VHDL -> Verilog 변경※) -> OK

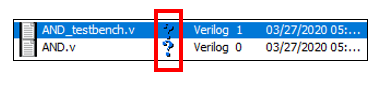

추가된 파일을 확인 - AND_testbench.v

마찬가지로 추가된 파일을 더블 클릭하면

코드를 작성할 수 있는 공간이 생성됨

Verilog_testbench 코드 작성

`timescale 1ns / 1ns // 시간설정 (단위 / 해상도[정밀체크시 ex(1ns/100ps)])

module testbench; // 모듈 선언 및 이름

reg A,B; // 전달받을 데이터를 저장 (계속 사용)

wire Y; // 전달받을 데이터를 저장하지않음 (일회성)

AND chip_and(A,B,Y); // AND모듈호출, 호출이름:chip_and, 인풋아웃풋

initial // 구문으로 순차적으로 신호를 인가할 때 사용 (한번만 수행)

begin // 구문 시작 {

A=0;B=0;#50; // #50ns 뒤에 A단자로 0입력, B단자로 0입력 (현재시간 0ns)

A=0;B=1;#50; // #50ns 뒤에 A단자로 0입력, B단자로 1입력 (현재시간 50ns)

A=1;B=0;#50; // #50ns 뒤에 A단자로 1입력, B단자로 0입력 (현재시간 100ns)

A=1;B=1;#50; // #50ns 뒤에 A단자로 1입력, B단자로 1입력 (현재시간 150ns)

end // 구문 종료 }

endmodule // 모듈 종료

Verilog언어로 코드를 작성 후 Ctrl+s를 눌러 저장

AND_testbench모듈을 설계하였다.

저장이 완료되었다면 파일이름의 * 표시가 사라짐

Compile(상단 탭) -> Compile All 클릭하여 컴파일

(컴파일 - 입력 창의 텍스트 데이터를 Verilog 언어 데이터로 변환)

컴파일이 완료되면 ? -> √ 처럼 기호가 바뀜

// 에러가 출력될 경우 코드 작성에서 실수한 부분이 있을 것 //

// 에러 Log를 더블클릭하여 읽고 문제 코드를 수정 //

컴파일된 코드 AND모듈을 테스트벤치로 시뮬레이션

시뮬레이션 경로 : Simulate(상단 탭) -> Start Simulation

시뮬레이션 설정 : Work[+]탭 확장 -> Ctrl + (AND, testbench) 선택 -> OK

시뮬레이션 파형 보기 : Simulation 생성 완료 -> testbench 마우스 우측 클릭 -> add wave 클릭

① 테스트벤치 파형 측정을 50ns * 4 = 200ns 로 설계하였음으로

② 확대버튼을 3번 눌러 측정 단위를 낮춰줌

① 측정 단위가 200ns 인것을 확인

② Run 버튼을 눌러 100ns 단위로 파형 측정을 시작

③ 버튼을 한번 더 눌러 200ns 측정

테스트벤치 입력을 AND모듈에 적용한 시뮬레이션 파형 결과 확인

시뮬레이션 파형결과 출력

(첫번째 사진 ①마크 왼쪽) Cursor 1 우클릭으로 커서값을 조정

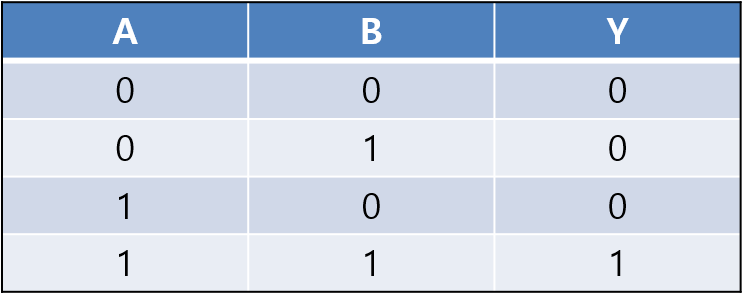

출력파형 결과

① 25ns 일때 파형 값은 A=0, B=0, Y=0

② 75ns 일때 파형 값은 A=0, B=1, Y=0

③ 125ns 일때 파형 값은 A=1, B=0, Y=0

④ 175ns 일때 파형 값은 A=1, B=1, Y=1

테스트벤치에서 인가한 신호가 잘 출력되었음을 결과로 확인

AND모듈을 거쳐 생성된 Y값이 정상적인지 AND모듈의 진리표를 확인할 예정

AND모듈의 진리표와 출력파형 결과가 일치함을 확인

시뮬레이션 종료 : 하단 Transcript에 quit -sim 입력

-END-

다음 장은 각 디지털 모듈들을 설계..?를 할 예정